# CM1K NEUROMORPHIC CHIP

The CM1K is a **neuromorphic chip** opening new frontiers for smart sensors and cognitive computing applications. It can solve pattern recognition problems from text and data analytics, vision, audition, and multi-sensory fusion with orders of magnitude less energy and complexity than modern microprocessors.

The CM1K chip features 1024 interconnected neurons working in parallel and capable of learning and recognizing patterns in a few microseconds. The neurons behave collectively as a K-Nearest Neighbor classifier or a Radial Basis Function and are trainable. They are especially suitable to cope with ill-defined and fuzzy data, high variability of context and even novelty detection. Last, but not least, multiple CM1K chips can be daisy-chained to scale a network from thousands to millions of neurons with the same simplicity of operation as a single chip.

## **BRAIN-INSPIRED BEHAVIOR**

- All neurons have the same behavior. They receive and execute the same instructions in parallel.

- All neurons are interconnected. The "winner-takes-all" and novelty (in the absence of winner) can trigger autonomous learning. Confusion can be corrected.

- The neurons can behave as a K-Nearest Neighbor (KNN) classifier or a Radial Basis Function (RBF).

- Patterns are broadcasted to all neurons at once, whether for learning or recognition.

- Recognition and learning latencies are constant, in the order of micro-seconds per pattern and independent of the number of neurons in use.

- Neurons are trained by example and decide autonomously when it is necessary to commit a new neurons and/or correct their own firing threshold (influence field)

- The knowledge built autonomously by the neurons can be saved and restored

## **BRAIN-INSPIRED ARCHITECTURE**

- CM1K has a patented parallel architecture with no controller or supervisor

- It operates at low frequency (16-27 Mhz) and dissipates only 0.5 Watts

### **OPERATIONS**

- Simple Register Transfer Level instruction set based on 15 registers

- Optional serial I2C port

- Optional digital input bus to broadcast patterns to a simple recognition stage

## CONNECTIVITY

- All neurons are interconnected though a small bidirectional bus (26 lines) both internally and externally

- Multiple CM1K chips can be easily daisy-chained to build networks with 1024 neurons increment

- All neurons have the same behavior whether they belong to a same single chip or a chain of chips

**康普企業有限公司** 台北市和平西路二段141 號6 樓之4 Email: CECL@seed.net.tw http://www.compton.com.tw Tel: (02) 2314-2018, 2381-7255 Mobile: 0928-812-548

Image recognition

- Machine vision

Target tracking

- Video monitoring

- Medical and satellite imaging

- Smart motion, ...

#### Signal recognition

- Speech recognition

- Voice identification

- Sonar, Radar identification

- EKG, EEG analysis

- Vibration monitoring,...

#### Data mining

- Bioinformatics Fingerprint identification

- Cyber security

- Sentiment analytics

- Graphing,...

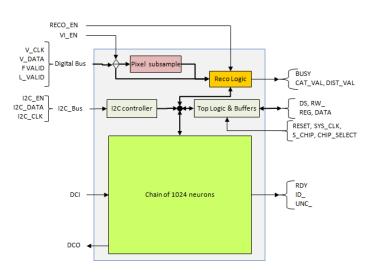

The CM1K chip is a chain of 1024 identical neurons operating in parallel, but also interconnected together to make global decisions. A neuron is a memory with some associated logic to compare an incoming pattern with the reference pattern stored in its memory and react (i.e. fire) according to its similarity range. A neuron also has a couple of attribute registers such as a context and category value. Once a pattern is broadcasted, the neurons communicate briefly with one another (for 16 clock cycles) to determine which one holds the closest match in its memory. The "Winner-Takes-All" neuron de-activates itself when its category is read, thus leaving the lead to the next "Winner-takes-All", if applicable, and so on.

A single CM1K matching a pattern of 256 bytes against 1024 models delivers the equivalent of 192 GiGaOps per second.

Learning is initiated by simply broadcasting a category after an input pattern. If it represents novelty, the next neuron available in the chain automatically stores the pattern and its category. If some firing neurons recognize the pattern but with a category other than the category to learn, they auto-correct their influence fields. This intrinsic inhibitory and excitatory behavior makes the CM1K chip a unique component for cognitive computing applications.

Furthermore, CM1K integrates a built-in recognition engine which can receive vector data directly through a digital input bus, broadcast it to the neurons and return the best-fit category 3 microseconds later. In the case of a video input signal, NeuroMem can optionally extract a 1D vector from 2D video data.

| Timings in μs                           | Single CM1K @27Mhz | Chain of CM1K @16Mhz |            |

|-----------------------------------------|--------------------|----------------------|------------|

| vector of 256 bytes                     |                    |                      | Vector/sec |

| Broadcast and Read status               | 9.59               | 16.19                | 61776      |

| Broadcast and Read Best match           | 10.93              | 18.44                | 54237      |

| Broadcast and Read 5 nearest neighbors  | 16.41              | 27.69                | 36117      |

| Broadcast and Read 20 nearest neighbors | 36.96              | 62.38                | 16032      |

| ANN Attributes     | СМ1К                         |

|--------------------|------------------------------|

| Neuron capacity    | 1,024                        |

| Neuron memory size | 256 bytes                    |

| Categories         | 15 bits                      |

| Distances          | 16 bits                      |

| Contexts           | 7 bits                       |

| Recognition status | Identified, Uncertain or     |

|                    | Unknown                      |

| Classifiers        | Radial Basis Function (RBF)  |

|                    | K-Nearest Neighbor (KNN)     |

| Distance Norms     | L1 (Manhattan)               |

|                    | Lsup                         |

| Logic module       | High speed recognition stage |

| (optional)         | (for 1D & 2D vector data)    |

| Electrical and IOs | СМ1К                                |

|--------------------|-------------------------------------|

| Clock frequency    | 27MHz for single chip               |

|                    | 16 Mhz for chain of multiple chips  |

| I/O                | Parallel bus (26 lines)             |

|                    | Serial I2C @100 and 400 Kbit/sec    |

|                    | Digital input bus (optional use, 11 |

|                    | lines for data and sync signals)    |

| Process & Die-size | 130nm / 64 sq.millimeter            |

| Electrical         | 3.3 V I/O operation 1.2 V core      |

|                    | I static 260mA                      |

| Power              | <300 mW in active mode (CS_ low)    |

| consumption        | at 1.2V and 3.3V                    |

| Package            | 100-pin TQFP 14x14mm package        |